Samsung verschiebt 1,4-nm-Chips und setzt auf 2/4-nm. High-NA-EUV verzögert sich, mit Folgen für Technik- und Wirtschaftsentscheider. Jetzt weiterlesen!

Inhaltsübersicht

Einleitung

Branchenbeben: Warum Samsung das 1,4-nm-Rennen stoppt

High-NA-EUV erklärt: Technik, Tücken und Wendepunkte

Impact: Was die Verzögerung für Tech & Wirtschaft bedeutet

Chip-Zukunft auf Zeit: Chancen, Risiken und Spielräume

Fazit

Einleitung

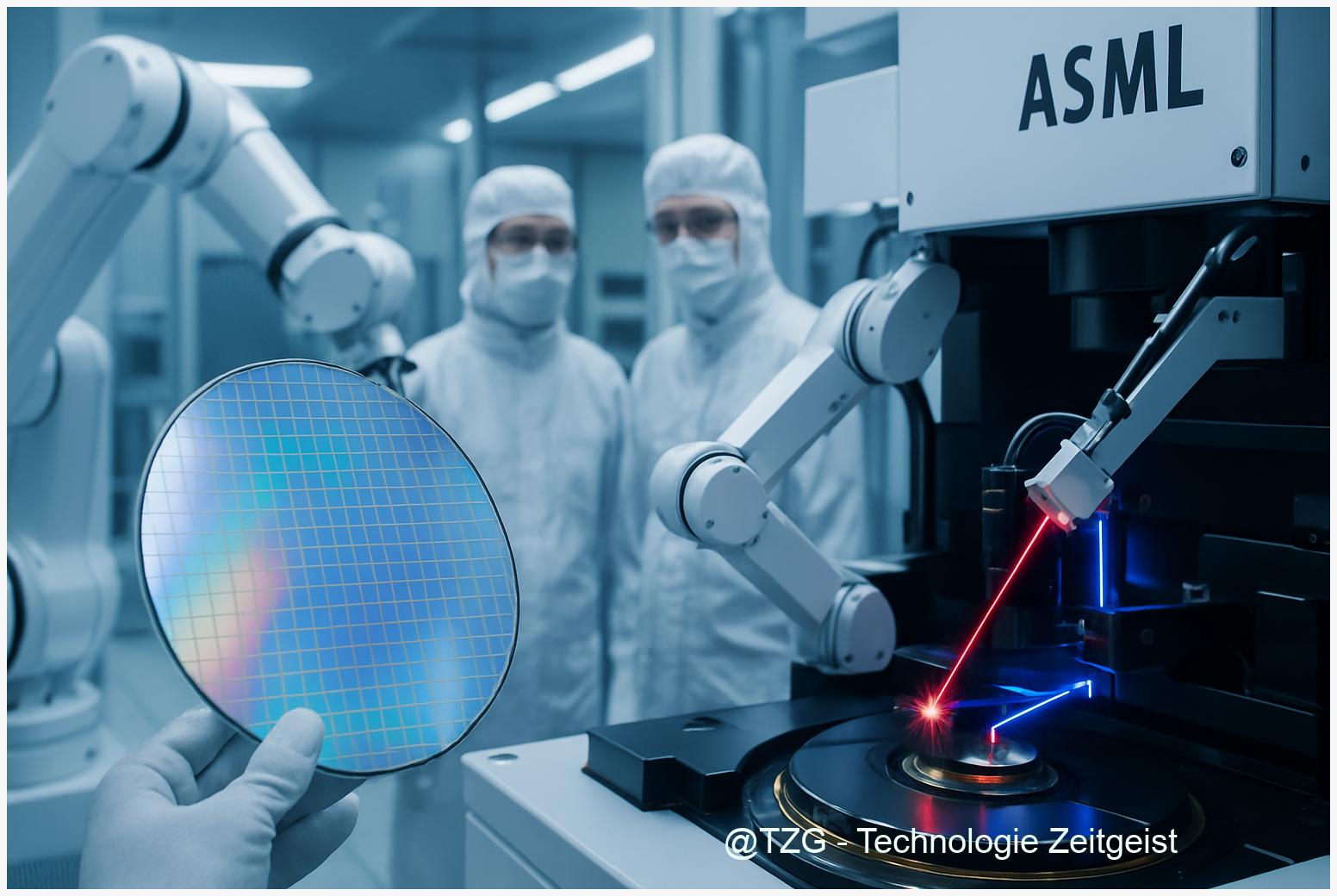

Was passiert, wenn die Halbleiter-Industrie auf die Bremse tritt? Samsung hat die Produktion seiner revolutionären 1,4-nm-Chips zurückgestellt und priorisiert stattdessen eine Optimierung der 2- und 4-nm-Ausbeute. Gleichzeitig signalisiert der Ausrüster ASML, dass auch andere Branchengrößen den Einsatz der fortschrittlichen High-NA-EUV-Scanner verschieben. Diese Entwicklung sendet Schockwellen durch eine Industrie, die bislang im Rekordtempo auf immer kleinere Strukturgrößen und leistungsfähigere Chips zusteuerte. Im Fokus stehen Tech-Entscheider, die Effizienzgewinne und Investitionssicherheit erwarten. Der Artikel beleuchtet zunächst das aktuelle Marktgeschehen, entwirrt technische Hintergründe rund um die High-NA-EUV-Technologie und analysiert die konkreten Auswirkungen auf Lieferketten und Wettbewerb. Abschließend diskutieren wir, wie sich die angezogene Handbremse auf die künftige Dynamik der Chipbranche auswirkt.

Branchenbeben: Warum Samsung das 1,4-nm-Rennen stoppt

Die Entwicklung des Samsung 1,4-nm-Chip ist ins Stocken geraten: Branchenberichte von DIGITIMES bestätigen, dass Samsung die Einführung der 1,4-nm-Strukturbreite verschiebt und stattdessen seine Ressourcen auf die Optimierung der 2-nm-Halbleiterfertigung bündelt. Diese Entscheidung sendet ein starkes Signal in die Branche – und rückt die Herausforderungen rund um High-NA-EUV und neue Lithographie-Technologien ins Zentrum des globalen Wettbewerbs.

Fokus auf Ausbeute statt Rekorde: Die neue Samsung-Roadmap

Laut DIGITIMES und TrendForce hat Samsung den Start der 1,4-nm-Produktion auf frühestens 2027 verschoben. Grund sind technische Hürden bei der Ausbeute – also dem Anteil funktionierender Chips pro Wafer. Mit dem Schritt folgt Samsung nicht nur dem Ruf nach verlässlicheren Prozessen, sondern positioniert sich im Wettbewerb mit TSMC und Intel, die ihre eigenen Roadmaps ebenfalls anpassen. TSMC plant, High-NA-EUV (High Numerical Aperture Extreme Ultraviolet Lithography) erst mit dem 1-nm-Knoten einzusetzen, während Intel die neue Lithographie bereits mit seinem 14A-Knoten erprobt. Die Branche setzt also auf Stabilität, nicht Geschwindigkeit.

High-NA-EUV: Hoffnungsträger und Stolperstein zugleich

ASML, als einziger Anbieter von High-NA-EUV-Anlagen, sieht die Technologie weiterhin als Schlüssel für die nächsten Strukturgrößen. Doch selbst ASML räumt laut DIGITIMES ein: Die hohen Investitionskosten (über 370 Mio. USD pro Maschine) und technische Risiken bremsen die Einführung. Samsung wird sein erstes High-NA-EUV-System zwar ab Ende 2024 zu Testzwecken installieren (Tom’s Hardware), aber der industrielle Einsatz rückt auf Mitte bis Ende des Jahrzehnts. Im Speichergeschäft verzichtet Samsung vorerst auf High-NA-EUV – künftige 3D-DRAM-Architekturen kommen ohne diese Technik aus.

Globale Dynamik: Warten auf den Durchbruch

Die Verschiebung des Samsung 1,4-nm-Chip ist mehr als eine Roadmap-Anpassung: Sie unterstreicht, wie eng technische, wirtschaftliche und geopolitische Faktoren in der Halbleiterfertigung verwoben sind. Während die Nachfrage – etwa durch KI und Rechenzentren – weltweit wächst, wägen die Entscheider den richtigen Zeitpunkt für kostspielige Investitionen ab. Wer das Gleichgewicht zwischen Pioniergeist und Fertigungssicherheit findet, prägt die Zukunft der Branche.

Im nächsten Kapitel erklären wir, wie High-NA-EUV funktioniert, welche technischen Hürden bestehen – und warum der große Durchbruch auf sich warten lässt.

High-NA-EUV erklärt: Technik, Tücken und Wendepunkte

Der Sprung zum Samsung 1,4-nm-Chip verlangt nach Präzision auf atomarer Ebene – und stellt die Halbleiterfertigung vor nie dagewesene Herausforderungen. Im Zentrum steht die High-NA-EUV-Lithografie, eine Technik, die bei Strukturbreiten im Bereich von 1,4 nm neue Maßstäbe setzt. Doch wie funktioniert diese Technologie, und warum stößt sie an technische Grenzen?

Scanner-Prinzip: Von klassischer zu High-NA-EUV

Der Lithografiescanner ist das Herzstück der Chipfertigung. Hier projiziert ultraviolettes Licht – im Fall von EUV mit einer Wellenlänge von 13,5 nm – das Schaltkreismuster auf einen Siliziumwafer. “Numerische Apertur” (NA) beschreibt dabei, wie fein das System Strukturen abbilden kann. High-NA-EUV erhöht diesen Wert von 0,33 auf 0,55. Das Ergebnis: Die Auflösung steigt von rund 13,5 nm auf etwa 8 nm. Eine Analogie: Statt mit einem dicken Filzstift (klassische EUV) arbeitet der Scanner mit einer extrem feinen Feder (High-NA-EUV). Das ermöglicht kleinere, dichtere Strukturen – entscheidend für den Samsung 1,4-nm-Chip.

Technische Tücken: Ausbeute, Masken und Belichtung

Mit der höheren Auflösung wachsen die technischen Hürden. Die “Ausbeute” – der Anteil fehlerfreier Chips pro Wafer – sinkt, sobald kleinste Defekte ganze Schaltungen unbrauchbar machen. Der Belichtungsprozess erfordert neue, dünnere Photoresists (lichtempfindliche Beschichtungen), die nur schwer gleichmäßig aufgetragen werden können. Die Masken, die das Schaltkreismuster übertragen, müssen für High-NA-EUV neu entwickelt werden – sie sind anfälliger für Fehler und kostenintensiver. Zudem halbiert sich das Bildfeld: Pro Wafer muss nun doppelt so oft belichtet werden, was den Durchsatz reduziert und die Kosten je Chip erhöht.

Grenzen des Machbaren: Warum aktuelle Prozesse stocken

ASML, der einzige Hersteller von High-NA-EUV-Scannern, liefert Systeme wie die Twinscan EXE:5000 für über 350 Millionen Euro pro Stück. Erste Praxistests – etwa bei Intel für den 14A-Knoten – zeigen: Trotz besserer Auflösung kämpfen Hersteller mit geringem Durchsatz, Materialproblemen und erhöhtem Energiebedarf. Auch Samsung erlebt diese Hürden, was die Verzögerung beim Samsung 1,4-nm-Chip mitbedingt. Die Kombination aus steigenden Komplexitätskosten, empfindlichen Materialien und dem Zwang zu immer fehlerärmeren Prozessen bringt die Branche an den Rand des technisch Machbaren.

Im nächsten Kapitel nehmen wir in den Blick, wie die Verzögerung beim 1,4-nm-Knoten Wirtschaft und Technologiebranche beeinflusst – vom Innovationsdruck bis zu den globalen Lieferketten.

Impact: Was die Verzögerung für Tech & Wirtschaft bedeutet

Die Verschiebung beim Samsung 1,4-nm-Chip hat weitreichende Folgen für die gesamte Halbleiterfertigung. Während Samsung bislang als Innovationstreiber für moderne Strukturbreiten galt, sorgt die Verzögerung nun für Unsicherheit bei Kunden, Zulieferern und Investoren. Laut TweakTown und TechPowerUp wird der 1,4-nm-Knoten frühestens nach 2028 in die Massenproduktion gehen – ein Rückschlag für alle, die auf schnellere Skalierung setzen.

Risiken: Kundenverluste, längere Lieferzeiten und verschärfter Wettbewerb

Großkunden wie Google wechseln bereits zu TSMC, das mit stabileren Prozessen und höheren Ausbeuten bei 2-nm- und 3-nm-Knoten punktet. Die Folge: Samsungs Marktanteil im Foundry-Geschäft sinkt auf rund 8 Prozent, während TSMC über 67 Prozent hält. Zulieferer müssen sich auf schwankende Abnahmemengen einstellen; längere Lieferzeiten und unsichere Investitionszyklen bremsen Innovationen entlang der gesamten Wertschöpfungskette. Investitionen in neue High-NA-EUV-Anlagen werden bei Samsung gekürzt – 2025 halbiert sich das Budget gegenüber dem Vorjahr auf 5 Billionen KRW.

Chancen und kritische Sektoren: KI, Automotive und HPC im Fokus

Für Anwendungen in künstlicher Intelligenz, High-Performance Computing (HPC) und Automotive-Chips bedeuten Verzögerungen beim Samsung 1,4-nm-Chip weniger Spielraum bei Performance und Energieeffizienz. Gerade in diesen Sektoren entscheidet der Zugang zu modernsten Strukturbreiten über Wettbewerbsfähigkeit. Gleichzeitig eröffnet der Fokus auf 2-nm- und 3-nm-Prozesse Chancen, bestehende Technologien zu optimieren und Ertragsprobleme zu lösen. ASML als Lieferant für High-NA-EUV-Scanner bleibt Schlüsselpartner, doch die Nachfrage nach neuen Anlagen verlagert sich – mit Auswirkungen auf das gesamte Ökosystem.

Globale Marktvolumen und Prognosen

Das weltweite Marktvolumen für Halbleiterfertigung stieg 2023 auf über 600 Mrd. USD, doch die Unsicherheit bei der Einführung neuer Strukturbreiten wirkt sich bereits auf Prognosen bis 2028 aus. Lieferverzögerungen und verschobene Investitionsentscheidungen treffen besonders Wachstumsbranchen wie KI und 5G/6G-Kommunikation. Entscheider müssen jetzt flexibel agieren, Partnerschaften ausbauen und die technologische Roadmap neu bewerten.

Im nächsten Kapitel analysieren wir, wie die Branche trotz Unsicherheit Spielräume auslotet – und warum der Wettlauf um die Zukunft der Chipfertigung offen bleibt.

Chip-Zukunft auf Zeit: Chancen, Risiken und Spielräume

Die verschobene Roadmap für den Samsung 1,4-nm-Chip sendet Schockwellen durch die Halbleiterfertigung. Während Samsung die Einführung auf mindestens 2027 vertagt, ringen Intel und TSMC mit eigenen Strategien, um das Rennen um Strukturbreite und Effizienz nicht zu verlieren. Die Branche steht vor einem Balanceakt zwischen Innovationsdruck, Risiken und dem Erhalt globaler Lieferketten.

Strategiewechsel: Von Roadmaps zu Resilienz

Samsung priorisiert jetzt den sogenannten 1-nm-“Dream-Prozess” für die Zeit nach 2029 und verlagert Investitionen auf den 2-nm-Knoten. Intel setzt mit seinem 14A-Prozess (1,4 nm) ab 2026/27 auf High-NA-EUV, will aber dank Partnerschaften und aggressiven Fertigungsplänen bis 2030 TSMC als zweitgrößter Foundry-Anbieter herausfordern. TSMC bleibt vorsichtig: High-NA-EUV wird erst zur 1-nm-Generation ab etwa 2029/30 breit eingesetzt. Statt auf riskante Sprünge setzt TSMC auf stabile Prozesse bei 1,6 und 1,4 nm und optimiert bestehende Fertigungslinien.

Risiken, Innovationspotenziale und Engpässe

Die Verzögerung beim Samsung 1,4-nm-Chip birgt Risiken für Marktanteile und Investitionen. High-NA-EUV-Scanner von ASML sind teuer (über 350 Mio. EUR pro System), rar und unterliegen Exportbeschränkungen. Lieferkettenengpässe drohen insbesondere bei AI- und HPC-Chips, wo kleinste Strukturbreiten entscheidend sind. Gleichzeitig entstehen neue Chancen: Innovationen wie Gate-All-Around-FETs, backside power delivery und AI-optimierte Designs verschieben den Wettbewerb – nicht nur um Strukturbreite, sondern auch um Energieeffizienz und Prozessstabilität. Investoren fokussieren zunehmend auf Diversifikation, regionale Kapazitäten und flexible Partnerschaften, um geopolitische Risiken besser abfedern zu können.

Alternative Fertigungskonzepte und Planungsspielräume

Entscheider setzen verstärkt auf mehrgleisige Investitionsstrategien:

- Optimierung bestehender Knoten (2- und 3-nm) mit höheren Ausbeuten

- Fokussierung auf Spezialprozesse für KI, Automotive und Sensorik

- Ausbau regionaler Fertigungskapazitäten in den USA, Japan und Europa

Die technischen Grenzen bei Strukturbreiten und Belichtung führen dazu, dass Innovationspotenziale zunehmend aus Material- und Architekturinnovationen entstehen – nicht mehr allein aus der Verkleinerung.

Im Ausblick zeigt sich: Die Branche muss langfristig mit Unsicherheiten und Kapazitätsengpässen leben. Erfolgreich bleibt, wer Investitionen flexibel steuert, Partnerschaften pflegt und alternative Fertigungskonzepte mitdenkt. Im nächsten Abschnitt analysieren wir, welche Szenarien die Chip-Zukunft prägen – und wie Entscheider ihren Handlungsspielraum nutzen können.

Fazit

Die kurzfristige Bremsung bei 1,4-nm-Chips und High-NA-EUV verschiebt nicht nur die Roadmaps großer Hersteller, sondern bietet auch Raum für Kurskorrekturen in der Industrie. Entscheider sollten aktuelle Fertigungstrends und Lieferketten noch sorgfältiger beobachten und flexibel auf strukturprägende Technologiewechsel reagieren. Der Fokus auf Prozessoptimierung und alternative Innovationswege könnte sich nun als Schlüssel zur Absicherung erweisen. Wer sich proaktiv ausrichtet, gewinnt – auch wenn der nächste Durchbruch später kommt.

Jetzt Fachnewsletter abonnieren und alle Roadmap-Updates zuerst erhalten!

Quellen

Samsung slows the node race: yield over speed at 2nm, 4nm

1.4nm put on ice: Samsung reportedly reroutes foundry push to 2nm yield gains

ASML bets on High-NA EUV as Intel, TSMC, Samsung delay mass adoption over cost and risk

Samsung may start installing its first High-NA EUV litho tool in late 2024 | Tom’s Hardware

[News] Samsung Reportedly Revises High-NA EUV Plans: Limited Memory Use, Foundry Begins at 1.4nm | TrendForce News

2025 semiconductor industry outlook | Deloitte Insights

News Posts matching ‘high-NA’ | TechPowerUp

Lithography – PRADEEP’s TECHPOINTS

European semiconductor industry – PRADEEP’s TECHPOINTS

What is the smallest size achievable with lithography for creating integrated circuits? – Quora

Volume Table of Contents – SPIE Digital Library

Samsung delays bleeding-edge 1.4nm node, puts its semiconductor eggs into its 2nm process

Samsung Foundry in Trouble, Might Cancel 1.4 nm Node High-Volume Manufacturing

Samsung Rumored To Have Cancelled Its Next-Generation 1.4nm Manufacturing Process

Samsung’s 1.4nm process development reportedly at standstill

[News] Samsung Rumored to Mull on Scrapping 1.4nm Node to Prioritize 2nm/3nm Yield Gains

Intel Unveils 1.4nm Chip Production Plan, Aims to Rival TSMC Dominance

News tagged TSMC at DIGITIMES

Samsung Electronics Begins Development of 1nm, the ‘Dream Semiconductor Process’

Samsung Unveils Chip Technology Road Map to Win AI Business

ASML bets on High-NA EUV as Intel, TSMC, Samsung delay mass adoption over cost and risk

TSMC unveils 1.6nm process technology with backside power delivery

[News] Decipher TSMC’s Calm Take on High-NA EUV Lithography Machines: Who May Have the Last Laugh in the Angstrom Era?

News Posts matching ‘1.4 nm’ | TechPowerUp

Unlocking the Future: TSMC’s Bold Strategy for the 2nm Revolution!

Hinweis: Für diesen Beitrag wurden KI-gestützte Recherche- und Editortools sowie aktuelle Webquellen genutzt. Alle Angaben nach bestem Wissen, Stand: 6/27/2025

Schreibe einen Kommentar